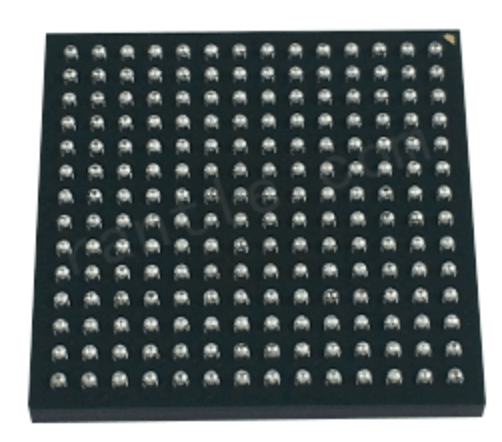

What Are NAND FLASH ICs: The Ultimate Guide

NAND Flash Integrated Circuits (ICs) are the backbone of modern non-volatile storage, enabling devices from USB drives to enterprise SSDs. Retaining data without power, NAND Flash balances cost, density, and performance, evolving through innovations like 3D stacking. This guide explores its structure, types, applications, and future trends.

1. Basic Structure and Operation

Floating-Gate Transistors

NAND Flash cells use floating-gate MOSFETs. Electrons trapped in the floating gate alter the transistor's threshold voltage, representing binary data (0 or 1).

NAND vs. NOR Architecture

NAND: Cells connected in series, enabling high density but slower random access. Ideal for bulk storage.

NOR: Parallel cell connections allow faster reads, used for execute-in-place code storage.

2. Types of NAND Flash

SLC (Single-Level Cell)

1 bit/cell: Two voltage states.

Pros: High endurance (~100k P/E cycles), fast, reliable.

Cons: Expensive.

Use Cases: Industrial, automotive.

MLC (Multi-Level Cell)

2 bits/cell: Four voltage states.

Pros: Balanced cost/performance (~10k P/E cycles).

Cons: Lower endurance than SLC.

Use Cases: Consumer SSDs.

TLC (Triple-Level Cell)

3 bits/cell: Eight voltage states.

Pros: Cost-effective (~3k P/E cycles).

Cons: Slower, requires robust ECC.

Use Cases: Budget SSDs, USB drives.

QLC (Quad-Level Cell)

4 bits/cell: Sixteen voltage states.

Pros: Highest density (~1k P/E cycles).

Cons: Lowest endurance, slower writes.

Use Cases: Mass storage (e.g., data centers).

3. Architecture

Planar vs. 3D NAND

Planar (2D): Traditional layout; limited by scaling.

3D NAND: Vertical stacking (e.g., Samsung’s V-NAND) boosts density and reliability. Uses Charge Trap Flash (CTF) for scalability.

Hierarchy

Pages: Smallest readable/writable unit (4–16 KB).

Blocks: Comprise ~128–256 pages; erase operations occur here.

4. Key Components

Interfaces

SATA/PCIe/NVMe: Dictate throughput (NVMe offers lowest latency).

ONFI/Toggle Mode: Define communication protocols.

Controllers

Functions: Wear leveling, garbage collection, ECC (LDPC/BCH codes).

Over-Provisioning: Spare blocks enhance longevity.

5. Performance Factors

Endurance: SLC > MLC > TLC > QLC.

Data Retention: Degrades with temperature; QLC ~1 year at 40°C.

Speed: Write speeds drop with cell density (QLC slowest).

6. Applications

Consumer Electronics: Smartphones, SSDs.

Enterprise: High-endurance drives for data centers.

Automotive: SLC for reliability in extreme conditions.

7. Challenges

Scaling Limits: Electron tunneling challenges at smaller nodes.

Interference: Cell-to-cell issues in dense arrays.

Cost vs. Performance: Balancing QLC affordability with endurance.

8. Future Trends

Higher Layer Counts: 200+ layers in 3D NAND.

PLC (Penta-Level Cell): 5 bits/cell, despite lower endurance.

Advanced ECC: AI-driven error correction.

Alternative Technologies: MRAM/ReRAM for niche roles.

Conclusion

NAND Flash ICs revolutionize storage, driven by 3D stacking and controller advancements. While endurance and scaling pose challenges, ongoing innovations ensure their dominance in the storage landscape, from consumer gadgets to enterprise solutions.

Kevin Chen

Founder / Writer at Rantle East Electronic Trading Co.,Limited

I am Kevin Chen, I graduated from University of Electronic Science and Technology of China in 2000. I am an electrical and electronic engineer with 23 years of experience, in charge of writting content for ICRFQ. I am willing use my experiences to create reliable and necessary electronic information to help our readers. We welcome readers to engage with us on various topics related to electronics such as IC chips, Diode, Transistor, Module, Relay, opticalcoupler, Connectors etc. Please feel free to share your thoughts and questions on these subjects with us. We look forward to hearing from you!

Start With

Start With Include With

Include With