What is SERDES? The Backbone of High-Speed Data Communication

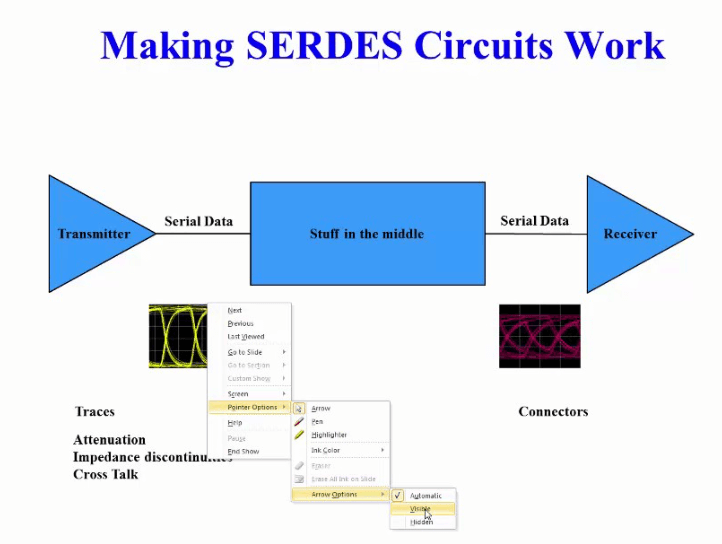

In the era of exponential data growth, SERDES (Serializer/Deserializer) technology has become indispensable for modern communication systems. As parallel interfaces struggled with limitations like signal skew, crosstalk, and physical space constraints, SERDES emerged as a solution to enable efficient, high-speed data transfer over serial links. By converting parallel data into a serial stream (and vice versa), SERDES minimizes the number of transmission channels while maximizing speed and reliability. This article explores the architecture, applications, and advancements of SERDES technology.

Core Functionality

SERDES operates through two primary components:

Serializer: Converts parallel data (multiple bits transmitted simultaneously) into a high-speed serial stream.

Deserializer: Reconstructs the serial stream back into parallel data at the receiving end.

Key Advantages Over Parallel Interfaces:

Reduced Pin Count: Fewer physical connections lower cost and complexity.

Higher Speeds: Serial links avoid timing skew issues inherent in parallel systems.

Long-Distance Compatibility: Serial transmission is less susceptible to noise over long distances.

Components of a SERDES System

Serializer

Uses a shift register to sequentially output parallel data bits.

Integrates a transmit clock (Tx Clock) to synchronize data output.

Deserializer

Reassembles serial data into parallel format using a receive clock (Rx Clock).

Often paired with Clock Data Recovery (CDR) to extract timing information from the data stream.

Clock Data Recovery (CDR)

Critical for synchronizing the receiver’s clock with the transmitter’s, especially in absence of a dedicated clock channel.

Utilizes phase-locked loops (PLLs) or delay-locked loops (DLLs).

Encoding/Decoding

8b/10b: Ensures DC balance and sufficient signal transitions for clock recovery (25% overhead).

64b/66b: Higher efficiency with minimal overhead (e.g., 100 Gigabit Ethernet).

PAM4: Pulse Amplitude Modulation with 4 levels, doubling data rates over traditional NRZ.

Framing & Alignment

Adds synchronization markers (e.g., start/stop bits) to manage data alignment.

Compensates for latency variations in multi-lane systems.

Applications of SERDES

Networking:

Ethernet (10G, 100G, 400G), Fibre Channel, and InfiniBand.

Telecommunications:

SONET/SDH for optical backbone networks.

Memory Interfaces:

DDR5 and GDDR6 use SERDES for high-speed data transfer.

Chip-to-Chip Communication:

PCI Express (PCIe 5.0: 32 GT/s per lane), SATA, and USB4.

Automotive:

ADAS sensors and in-vehicle infotainment systems.

Consumer Electronics:

HDMI 2.1 (48 Gbps) and DisplayPort.

Technical Challenges

Signal Integrity:

FFE (Feed-Forward Equalization) and DFE (Decision Feedback Equalization) mitigate inter-symbol interference (ISI).

At multi-gigabit speeds, attenuation, jitter, and EMI degrade signals.

Equalization Techniques:

Clock Synchronization:

CDR circuits must track frequency/phase variations accurately.

Power Consumption:

High-speed operation increases power dissipation, requiring low-power design strategies.

Interoperability:

Ensuring compatibility across standards (e.g., PCIe vs. Ethernet).

Recent Advancements

Higher Data Rates:

PCIe 6.0 (64 GT/s) and 800G Ethernet leverage PAM4 and advanced coding.

Optical Integration:

Co-packaged optics (CPO) combine SERDES with lasers for data center interconnects.

Embedded SERDES:

Integrated into ASICs and FPGAs for compact, low-latency designs.

Advanced Modulation:

PAM4 adoption in DDR5 and PCIe 6.0 doubles throughput per channel.

Conclusion

SERDES technology is the unsung hero behind the seamless operation of modern communication systems, enabling everything from hyperscale data centers to 8K video streaming. As data rates continue to soar with AI, 5G, and IoT, innovations like PAM4, co-packaged optics, and adaptive equalization will ensure SERDES remains at the forefront of high-speed design. Future developments may focus on terabit-scale transmission and energy-efficient architectures, further solidifying SERDES as a cornerstone of connectivity.

Kevin Chen

Founder / Writer at Rantle East Electronic Trading Co.,Limited

I am Kevin Chen, I graduated from University of Electronic Science and Technology of China in 2000. I am an electrical and electronic engineer with 23 years of experience, in charge of writting content for ICRFQ. I am willing use my experiences to create reliable and necessary electronic information to help our readers. We welcome readers to engage with us on various topics related to electronics such as IC chips, Diode, Transistor, Module, Relay, opticalcoupler, Connectors etc. Please feel free to share your thoughts and questions on these subjects with us. We look forward to hearing from you!

Start With

Start With Include With

Include With