Advanced Semiconductor Packaging Technology (2025)

Advanced Semiconductor Packaging Technology (2025)

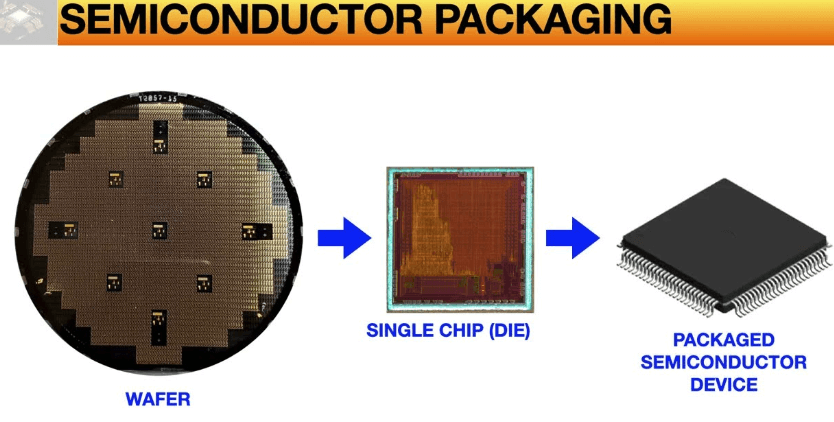

1. Introduction

Advanced Semiconductor Packaging Technology (ASPT) addresses the limitations of Moore's Law by enabling higher performance, miniaturization, and energy efficiency through innovative interconnects and material science. As of 2025, it has become a [ $72.6 , \text{billion} ] industry, driven by demand in AI, quantum computing, and IoT.

2. Core Technologies

2.1 3D/2.5D Integration

3D IC Stacking: Dies vertically connected using Through-Silicon Vias (TSVs) with [ \leq 5 , \mu\text{m} ] pitch.

Example: Samsung's 12-layer HBM3E (2024) achieves [ 1.2 , \text{TB/s} ] bandwidth.

2.5D Interposers: Silicon/glass interposers host multiple dies.

Case: AMD's MI300X uses a [ 4\text{-nm} ] interposer for CPU-GPU integration.

2.2 Fan-Out Wafer-Level Packaging (FOWLP)

Eliminates substrates by redistributing layers on molded wafers.

Key Players: TSMC's InFO-PoP (for mobile) and InFO_oS (for HPC).

2.3 System-in-Package (SiP)

Combines dies, passives, antennas, and sensors in one package.

Example: Apple's M3 Ultra integrates [ 134 , \text{billion} ] transistors using SiP.

2.4 Embedded Die Technologies

Dies embedded in organic substrates (e.g., ASE's ECPS for automotive radar).

3. Cutting-Edge Innovations (2024–2025)

3.1 Hybrid Bonding

Direct Cu-to-Cu bonding at [ <1 , \mu\text{m} ] pitch (Intel's Foveros Direct).

3.2 Chiplet Architectures

Modular design with Universal Chiplet Interconnect Express (UCIe) standard.

Example: Intel's Ponte Vecchio uses 47 chiplets.

3.3 Photonic-Electronic Integration

Co-packaged optics (CPO) for data centers (e.g., Broadcom's 1.6 Tb/s CPO modules).

4. Material Innovations

| Material | Application | 2025 Advancements |

|--------------------|--------------------------------------|-------------------------------------|

| Low-loss dielectrics | High-frequency 5G/6G | Ajinomoto's GX92 (Dk=3.2 @ 28 GHz) |

| Thermal interface | GPU/CPU cooling | Graphene-enhanced TIMs ([ 15 , \text{W/mK} ]) |

| Advanced substrates | High-density interconnects | Shinko's glass-core substrates |

5. Applications

AI/ML: NVIDIA's H200 GPU uses CoWoS-L packaging for [ 4.8 , \text{TB/s} ] memory bandwidth.

Quantum Computing: Cryogenic packaging for qubit control at [ 10 , \text{mK} ].

Medical IoT: Stretchable substrates for implantable biosensors.

6. Challenges

Thermal Management: Power densities exceeding [ 500 , \text{W/cm}^2 ] in 3D stacks.

Testing Complexity: Known-Good-Die (KGD) yield below [ 99.99% ] increases costs.

Standards Fragmentation: UCIe vs. OpenHBI vs. BoW interconnect protocols.

7. Future Outlook (2025–2030)

Sustainability: Biodegradable substrates (e.g., Panasonic's cellulose-based PKG).

Atomic-Level Bonding: Sub-nanometer alignment for quantum devices.

Neuromorphic Packaging: 3D integration mimicking biological neural networks.

8. Key Players

Foundries: TSMC, Samsung Foundry, Intel Foundry Services

OSATs: ASE Group, Amkor Technology

Material Suppliers: DuPont, Shin-Etsu

This technology is reshaping semiconductor roadmaps, enabling innovations from brain-computer interfaces to exascale computing.

Kevin Chen

Founder / Writer at Rantle East Electronic Trading Co.,Limited

I am Kevin Chen, I graduated from University of Electronic Science and Technology of China in 2000. I am an electrical and electronic engineer with 23 years of experience, in charge of writting content for ICRFQ. I am willing use my experiences to create reliable and necessary electronic information to help our readers. We welcome readers to engage with us on various topics related to electronics such as IC chips, Diode, Transistor, Module, Relay, opticalcoupler, Connectors etc. Please feel free to share your thoughts and questions on these subjects with us. We look forward to hearing from you!

Start With

Start With Include With

Include With