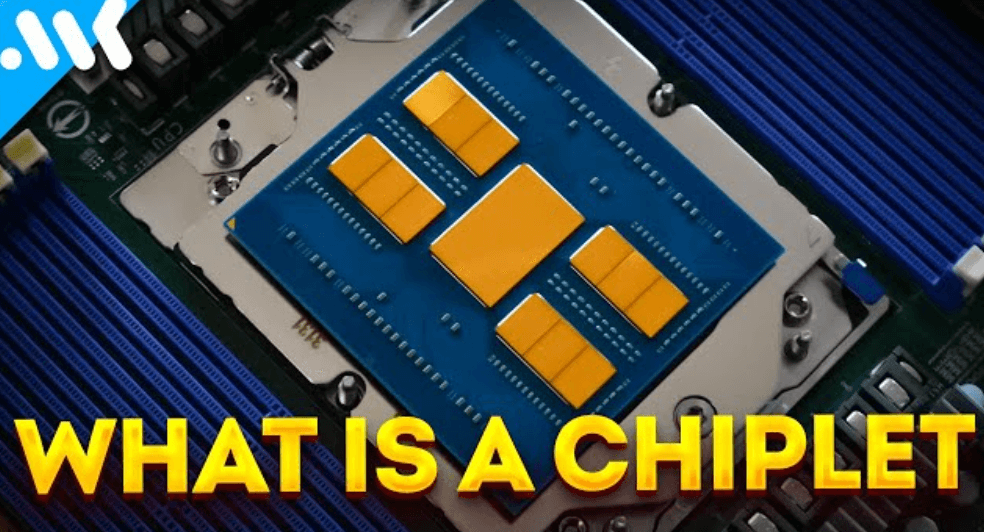

What is Chiplet? A Comprehensive Guide

The semiconductor industry has long thrived on Moore’s Law, the principle that transistor density doubles every two years. However, as transistor scaling approaches physical limits, the industry has turned to innovative architectures to sustain progress. Enter chiplets—a modular design paradigm redefining how integrated circuits (ICs) are built. This article explores the concept, benefits, challenges, and future of chiplets, offering insights into their transformative role in computing.

What Are Chiplets?

A chiplet is a small, modular semiconductor die designed to work cohesively with other chiplets within a single package. Unlike traditional monolithic ICs, where all components (CPU, GPU, I/O) reside on one die, chiplets disaggregate these functions into specialized blocks. These blocks are then integrated using advanced packaging technologies, enabling flexible, high-performance systems.

Key Architecture

Modular Design: Chiplets allow mixing and matching of dies optimized for different functions (e.g., compute, memory, I/O).

Interconnect Technologies:

2.5D Packaging: Chiplets are placed side-by-side on a silicon interposer (e.g., TSMC’s CoWoS, Intel’s EMIB), which routes signals between dies.

3D Packaging: Dies are stacked vertically using through-silicon vias (TSVs) for dense interconnects (e.g., TSMC-SoIC).

Universal Chiplet Interconnect Express (UCIe): A standardized open interface launched in 2022 by Intel, TSMC, Samsung, and others to enable cross-vendor interoperability.

How Do Chiplets Work?

Specialization: Each chiplet is fabricated using the optimal process node (e.g., 5nm for compute, 14nm for I/O).

Integration: Chiplets are bonded onto an interposer or substrate, connected via high-bandwidth interfaces (e.g., AMD’s Infinity Fabric).

Communication: High-speed die-to-die links (e.g., SerDes, TSVs) enable low-latency data transfer, mimicking monolithic performance.

Advantages of Chiplets

Cost Efficiency: Smaller dies improve yield rates, reducing manufacturing costs. For example, AMD’s Zen processors cut costs by 40% using chiplets.

Performance Gains: Leveraging best-in-class nodes for each function (e.g., 3nm for CPUs, older nodes for analog circuits).

Scalability: Systems can be scaled by adding more chiplets (e.g., adding memory chiplets for HPC workloads).

Heterogeneous Integration: Combining diverse technologies (e.g., Si photonics, GaN) in one package.

Sustainability: Reusing validated chiplets across designs reduces R&D costs and time-to-market.

Challenges

Design Complexity: Managing signal integrity, power delivery, and thermal dissipation across multiple dies.

Testing: Ensuring Known Good Die (KGD) reliability to prevent package-level failures.

Standardization: Fragmented ecosystems require UCIe-like standards to enable multi-vendor compatibility.

Thermal Management: Higher power density in 3D stacks risks overheating.

Security: Cross-chiplet communication may expose vulnerabilities in multi-vendor setups.

Applications

High-Performance Computing (HPC): AMD’s EPYC CPUs and Intel’s Ponte Vecchio GPU use chiplets for exascale computing.

AI Accelerators: NVIDIA’s Grace Hopper Superchip combines CPU and GPU chiplets for AI workloads.

Consumer Electronics: Apple’s M-series chips could adopt chiplets for customizable iPad/iPhone SOCs.

Automotive: Modular designs enable upgradable ADAS systems.

IoT: Cost-effective customization for edge devices.

Future Trends

UCIe Dominance: Widespread adoption of UCIe could create a “chiplet marketplace” for plug-and-play designs.

3D Integration: Advances in hybrid bonding will enable denser, faster stacks.

Quantum & Photonics Integration: Chiplets may incorporate quantum cores or optical I/O.

Democratization: Startups leveraging chiplets to compete with incumbents.

Conclusion

Chiplets represent a seismic shift in semiconductor design, offering a path beyond Moore’s Law through modularity and heterogenous integration. While challenges like standardization and thermal management remain, industry collaboration through UCIe and advancements in packaging herald a future where chiplets power everything from smartphones to supercomputers. As the ecosystem matures, chiplets will unlock unprecedented innovation, cementing their role as the cornerstone of next-gen electronics.

Kevin Chen

Founder / Writer at Rantle East Electronic Trading Co.,Limited

I am Kevin Chen, I graduated from University of Electronic Science and Technology of China in 2000. I am an electrical and electronic engineer with 23 years of experience, in charge of writting content for ICRFQ. I am willing use my experiences to create reliable and necessary electronic information to help our readers. We welcome readers to engage with us on various topics related to electronics such as IC chips, Diode, Transistor, Module, Relay, opticalcoupler, Connectors etc. Please feel free to share your thoughts and questions on these subjects with us. We look forward to hearing from you!

Start With

Start With Include With

Include With